The Intel 4002 Chip

The Intel 4002 chip was introduced in 1971 as part of the Intel 4000 family; a 320-bit MOS RAM and 4-bit output port, fabricated with P-channel silicon gate MOS technology

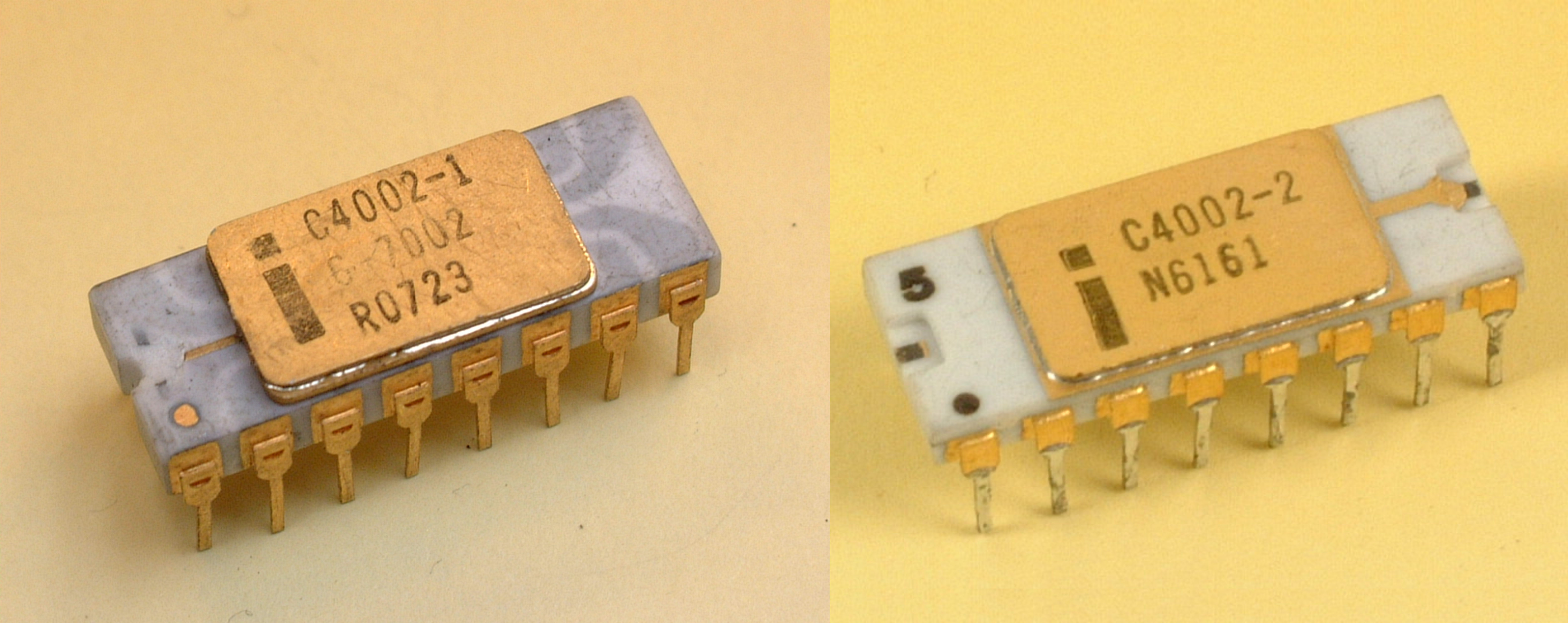

The 4002 was designed to be used with other MCS-4/40 devices such as the 4004 CPU. The chip was available in two different metal options 4002-1 and 4002-2 this was to make it possible to extend the chip selection so that 4pcs of 4002 chips could be connected to the 4004 CPU without any external chip selection logic. Although produced by Intel, National Semiconductors was the only second source.

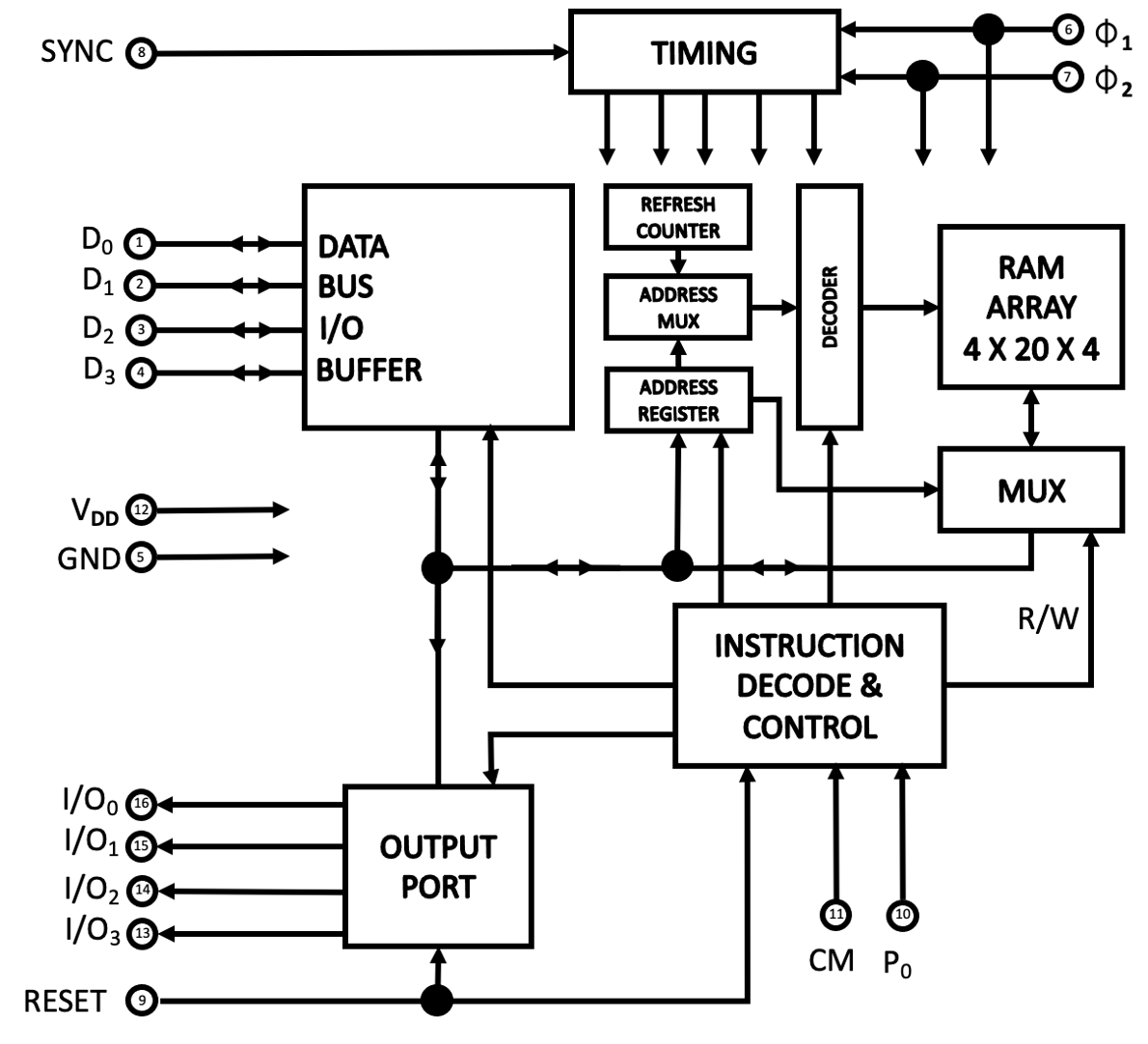

Logically, the Intel 4002 is set out as shown:

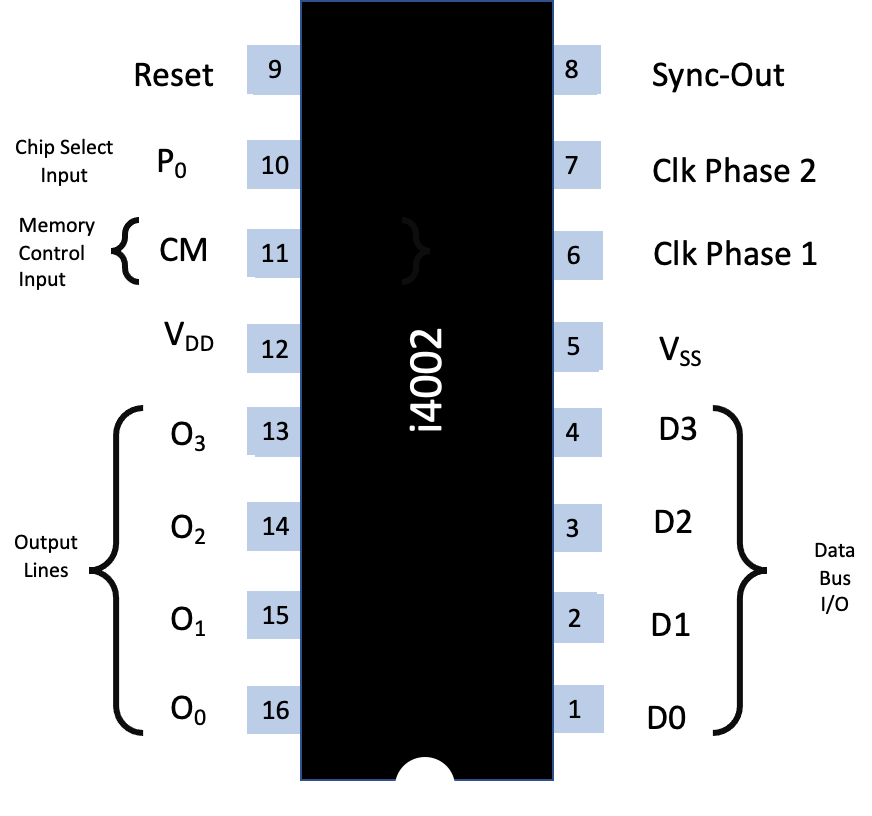

The circled numbers relate to the pins as shown below:

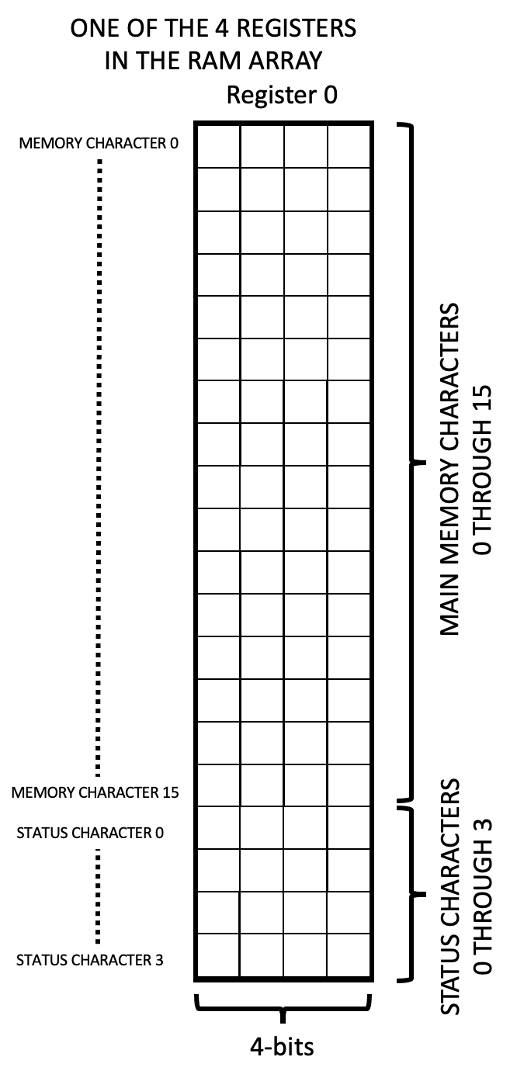

The 4002 performs two functions. As a RAM, it stores 320 bits arranged in 4 registers of 20 x 4-bit characters each (16 main memory characters and 4 status characters).

In the RAM mode, the operation is as follows: When the CPU executes an SRC instruction, it will send out the contents of the designated index register pair during X 2 and X 2 as an address to RAM, and will activate 1 CM-RAM line at X 2 for the previously selected RAM bank (see basic instruction cycle on page 5).

The data at X 2 and X 3 is interpreted as shown below:

As a vehicle for communication with peripheral devices, it is provided with 4 output lines and associated control logic to perform output operations.

The status character locations (0 through 3) are selected by the OPA portion of one of the I/O and RAM instructions.

For chip selection, the 4002 is available in two metal options, 4002-1 and 4002-2. An extra pin, P 0, (which may be hard wired to either V DD or V SS) is also available for chip selection.

The chip number is assigned as follows:

Chip # |

4002 Option |

P 0 |

D 3 @ X 2 |

D 2 @ X 2 |

|---|---|---|---|---|

0 |

4002-1 |

GND |

0 |

0 |

1 |

4002-1 |

V DD |

0 |

1 |

2 |

4002-2 |

GND |

1 |

0 |

3 |

4002-2 |

V DD |

1 |

1 |

Timing is internally generated using two clock signals X 1 and X 2, and a SYNC signal provided by the 4004. Internal refresh circuitry maintains data levels in the cells.

All communications with the system is through the data bus. The I/O port permits data out of the system. When the external RESET signal goes low, the memory and all static flip-flops (including the output registers) will be cleared. To fully clear the memory, the RESET signal must be maintained for at least 32 memory cycles (32 x 8 clock periods).

Note

Previously Selected Ram Bank

Bank switching is accomplished by the CPU after receiving a “DCL” (designate command line) instruction.

Prior to the execution of the DCL instruction the desired CM-RAM i code has been stored in the accumulator (for example,

through an LDM instruction). During DCL the CM-RAM 1 code is transferred from the accumulator to the CM-RAM register.

The RAM bank is then selected starting with the next instruction.